Posts

Finite impulse response (FIR) filters are useful for a variety of sensor signal processing applications, including audio and biomedical signal processing. Although several practical implementations for the FIR exist, the Direct Form Transposed structure offers the best numerical accuracy for floating point implementation. However, when considering fixed point implementation on a micro-controller, the Direct Form structure is considered to be the best choice by virtue of its large accumulator that accommodates any intermediate overflows.

This application note specifically addresses FIR filter design and implementation on a Cortex-M based microcontroller with the ASN Filter Designer for both floating point and fixed point applications via the Arm CMSIS-DSP software framework. Details are also given (including an Arm reference software pack) regarding implementation of the FIR filter in Arm/Keil’s MDK industry standard Cortex-M micro-controller development kit.

Introduction

ASN Filter Designer provides engineers with a powerful DSP experimentation platform, allowing for the design, experimentation and deployment of complex FIR digital filter designs for a variety of sensor measurement applications. The tool’s advanced functionality, includes a graphical based real-time filter designer, multiple filter blocks, various mathematical I/O blocks, live symbolic math scripting and real-time signal analysis (via a built-in signal analyser). These advantages coupled with automatic documentation and code generation functionality allow engineers to design and validate a digital filter within minutes rather than hours.

The Arm CMSIS-DSP (Cortex Microcontroller Software Interface Standard) software framework is a rich collection of over sixty DSP functions (including various mathematical functions, such as sine and cosine; IIR/FIR filtering functions, complex math functions, and data types) developed by Arm that have been optimised for their range of Cortex-M processor cores.

The framework makes extensive use of highly optimised SIMD (single instruction, multiple data) instructions, that perform multiple identical operations in a single cycle instruction. The SIMD instructions (if supported by the core) coupled together with other optimisations allow engineers to produce highly optimised signal processing applications for Cortex-M based micro-controllers quickly and simply.

ASN Filter Designer fully supports the CMSIS-DSP software framework, by automatically producing optimised C code based on the framework’s DSP functions via its code generation engine.

Designing FIR filters with the ASN Filter Designer

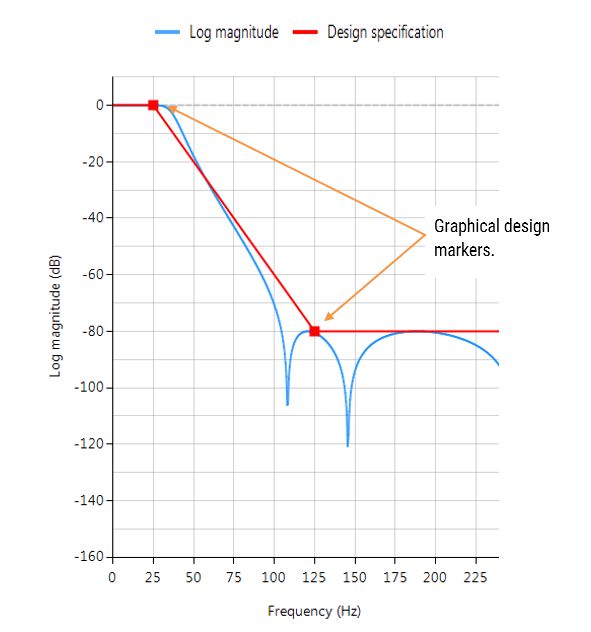

ASN Filter Designer provides engineers with an easy to use, intuitive graphical design development platform for FIR digital filter design. The tool’s real-time design paradigm makes use of graphical design markers, allowing designers to simply draw and modify their magnitude frequency response requirements in real-time while allowing the tool automatically fill in the exact specifications for them.

Consider the design of the following technical specification:

| Fs: | 500Hz |

| Passband frequency: | 0-25Hz |

| Type: | Lowpass |

| Method: | Parks-McClellan |

| Stopband attenuation @ 125Hz: | ≥ 80 dB |

| Passband ripple: | < 0.01dB |

| Order: | Small as possible |

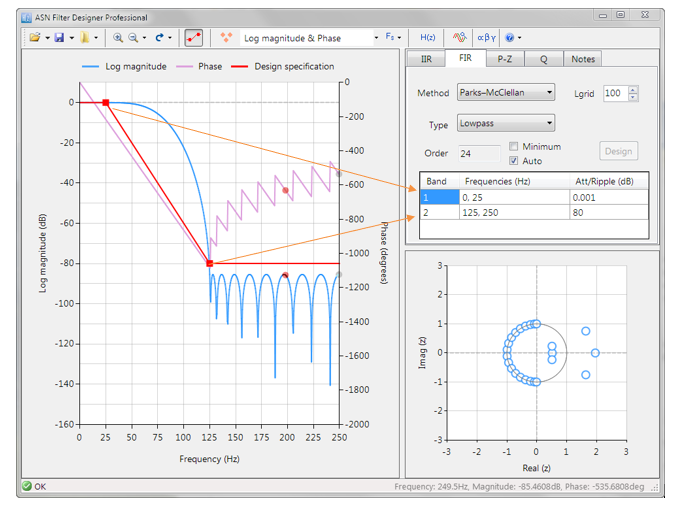

Graphically entering the specifications into the ASN Filter Designer, and fine tuning the design marker positions, the tool automatically designs the filter), automatically choosing the required filter order, and in essence – automatically producing the filter’s exact technical specification!

The frequency response of a filter meeting the specification is shown below:

This Lowpass filter will form the basis of the discussion presented herein.

Parks–McClellan algorithm

The Parks–McClellan algorithm is an iterative algorithm for finding the optimal Chebyshev FIR filter. The algorithm uses an indirect method for finding the optimal filter coefficients, that offers a degree of flexibility over other FIR design methods, in that each band may be individually customised in order to suit the designer’s requirements.

The primary FIR filter designer UI implements the Parks-McClellan algorithm, allowing for the design of the following filter types:

| Filter Types | Description |

| Lowpass | Designs a lowpass filter. |

| Highpass | Designs a highpass filter. |

| Bandpass | Designs a bandpass filter. |

| Bandstop | Designs a bandstop filter. |

| Multiband | Designs a multiband filter with an arbitrary frequency response. |

| Hilbert transformer | Designs an all-pass filter with a -90 degree phase shift. |

| Differentiator | Designs a filter with +20dB/decade slope and +90 degree phase shift. |

| Double Differentiator | Designs a filter with +40dB/decade slope and a +90 degree phase shift. |

| Integrator | Designs a filter with -20dB/decade slope and a -90 degree phase shift. |

| Double Integrator | Designs a filter with -40dB/decade slope and a -90 degree phase shift. |

These ten filter types provide designers with a great deal of flexibility for a variety of IoT applications. Design requirements may be simply specified via the use of the design markers. In all cases, the tool will automatically calculate the required filter order to meet the designer’s specification.

The Parks-McClellan algorithm is an optimal Chebyshev FIR design method. However, the algorithm may not converge for some specifications. In such cases, increasing the distance between the design marker bands generally helps.

Other FIR design methods

Designers looking to experiment with other types of FIR design methods may use the ASN FilterScript live symbolic math scripting language. The scripting language supports over 65 scientific commands and provides designers with a familiar and powerful programming language, while at the same time allowing them to implement complex symbolic mathematical expressions. The following functions are supported:

| Function | Description |

| movaver | Moving average FIR filter design. |

| firwin | FIR filter design based on the Window method. |

| firarb | Designs an FIR Window based filter with an arbitrary magnitude response. |

| firkaiser | Designs an FIR filter based on the Kaiser window method. |

| firgauss | Designs an FIR Gaussian lowpass filter. |

| savgolay | Design an FIR Savitzky-Golay lowpass smoothing filter. |

Please refer to the ASN FilterScript reference guide for more details.

All filters designed in ASN FilterScript are designed using double precision arithmetic in the H2 filter sandbox. An H2 filter must be transformed to an H1 (primary) filter for deployment.

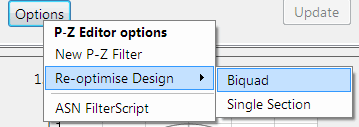

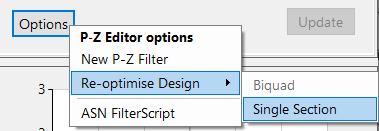

This may be simply achieved via the P-Z options menu:

The re-optimise method automatically analyses and converts the H2 filter into an H1 filter.

Floating point implementation

When implementing a filter in floating point (i.e. using double or single precision arithmetic) the Direct Form Transposed structure is considered the most numerically accurate. This can be readily seen by analysing the difference equations below (used for implementation), as the undesirable effects of numerical swamping are minimised, since floating point addition is performed on numbers of similar magnitude.

\(\displaystyle \begin{eqnarray}y(n) & = &b_0x(n) &+& w_1(n-1) \\ w_1(n)&=&b_1x(n) &+& w_2(n-1) \\ w_2(n)&=&b_2x(n) &+& w_3(n-1) \\ \vdots\quad &=& \quad\vdots &+&\quad\vdots \\ w_q(n)&=&b_qx(n) \end{eqnarray}\)

\(\displaystyle \begin{eqnarray}y(n) & = &b_0x(n) &+& w_1(n-1) \\ w_1(n)&=&b_1x(n) &+& w_2(n-1) \\ w_2(n)&=&b_2x(n) &+& w_3(n-1) \\ \vdots\quad &=& \quad\vdots &+&\quad\vdots \\ w_q(n)&=&b_qx(n) \end{eqnarray}\)

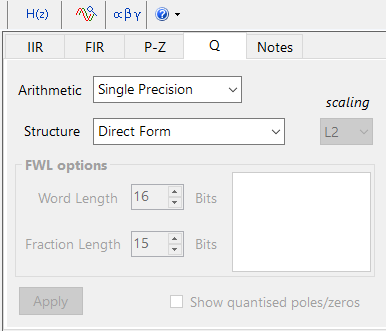

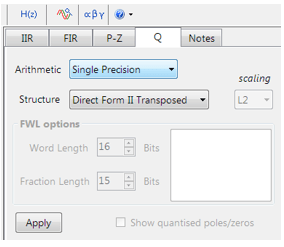

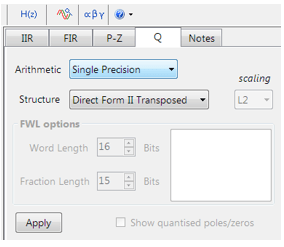

The quantisation and filter structure settings used to implement the FIR can be found under the Q tab (as shown below).

Despite the Direct Form Transposed structure being the most efficient for floating point implementation, the Arm CMSIS-DSP library does not currently support the Direct Form Transposed structure for FIR filters. Only the Direct Form structure is supported.

Setting Arithmetic to Single Precision and Structure to Direct Form and clicking on the Apply button configures the FIR considered herein for the CMSIS-DSP software framework.

The optimised functions within the Arm CMSIS-DSP framework currently support Single Precision arithmetic only.

Support for Double Precision and the Direct Form Transposed structure will be added in future releases.

Fixed point implementation

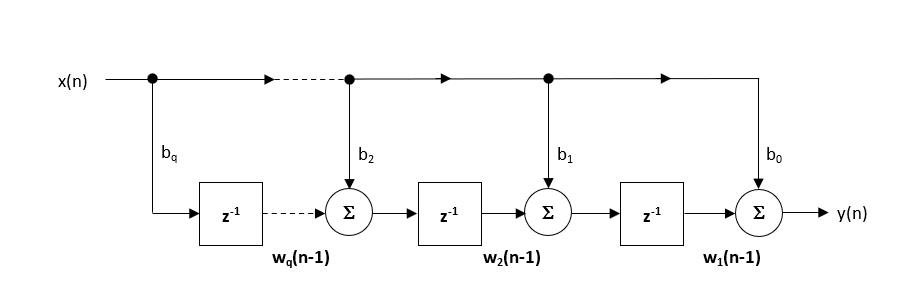

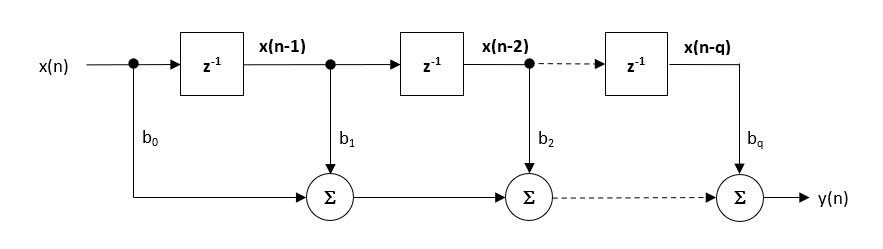

When implementing a filter with fixed point arithmetic, the Direct Form structure is considered to be the best choice by virtue of its large accumulator that accommodates any intermediate overflows. The Direct Form structure and associated difference equation are shown below.

\(\displaystyle y(n) = b_0x(n) + b_1x(n-1) + b_2x(n-2) + …. +b_qx(n-q) \)

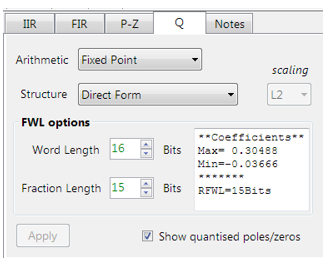

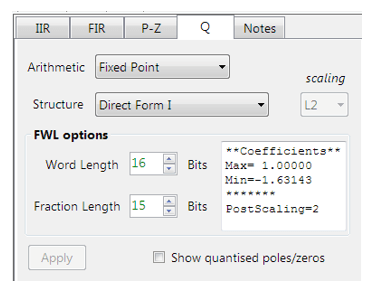

The CMSIS-DSP Framework supports Q7, Q15 and Q31 coefficient quantisation only. The options may be simply specified via the quantisation tab Q as shown below:

The tool’s inbuilt analytics (shown in the textbox) are intended to help the designer choose the most suitable quantisation settings.

As seen on the left, the tool has recommended a RFWL (recommended fraction length) of 15bits (Q15) for the coefficients, which is as required.

The Direct form structure is chosen over the Direct Form Transposed as a single (40-bit) accumulator can be used. The tool’s automatic code generator makes use of CMSIS-DSP’s 64-bit accumulators functions, so that the final C code deployed to a Cortex-M device will not overflow.

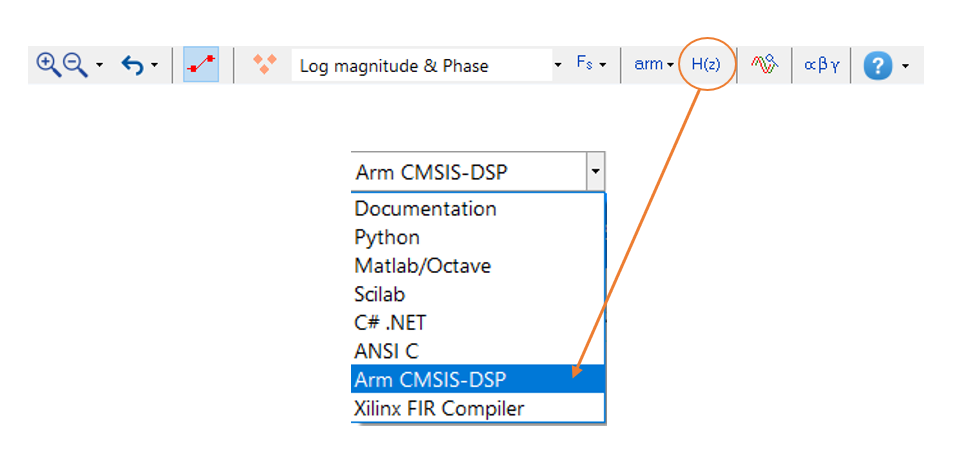

Deploying Arm CMSIS-DSP compliant code

The ASN Filter Designer’s automatic code generation engine facilitates the export of a designed filter to Cortex-M Arm based processors via the Arm CMSIS-DSP software framework. The tool’s built-in analytics and help functions assist the designer in successfully configuring the design for deployment.

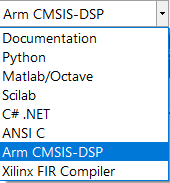

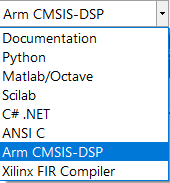

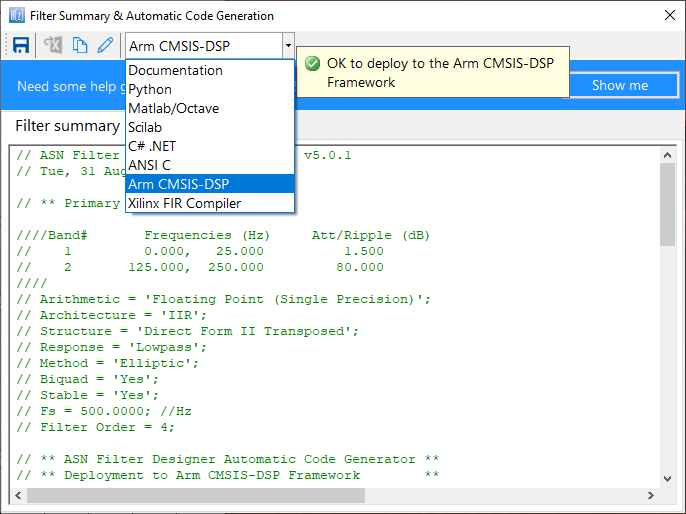

Select the Arm CMSIS-DSP framework from the selection box in the filter summary window:

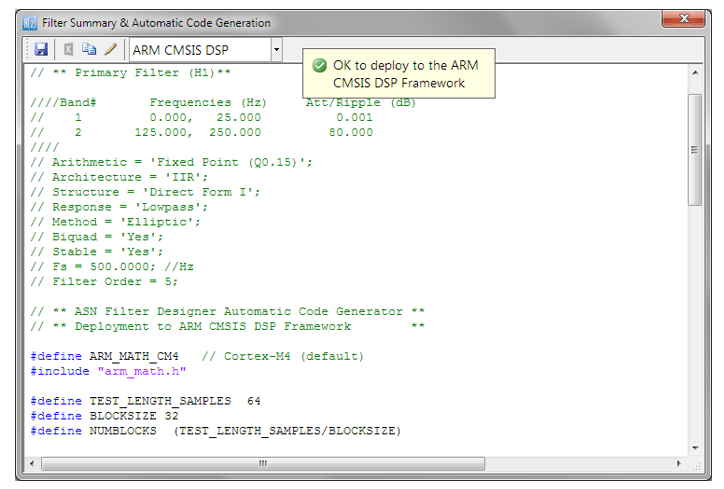

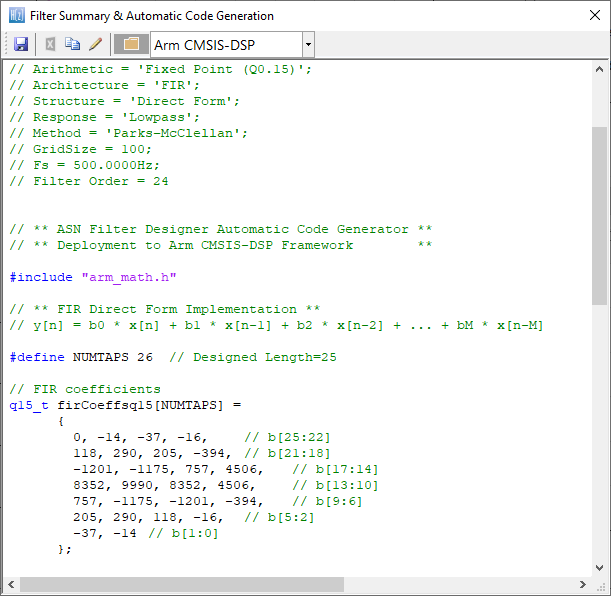

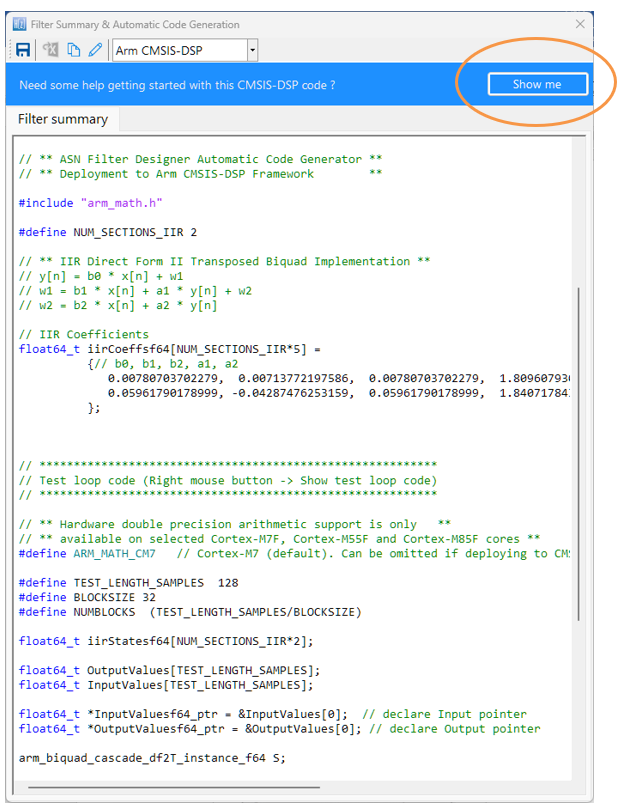

The automatically generated C code based on the Arm CMSIS-DSP framework for direct implementation on an Arm based Cortex-M processor is shown below:

This code may be directly used in any Cortex-M based development project.

Arm Keil’s MDK (uVision)

As mentioned above, the code generated by the Arm CMSIS DSP code generator may be directly used in any Cortex-M based development project tooling, such as Arm Keil’s industry standard uVision MDK (micro-controller development kit).

The following Arm software pack is available on Keil’s website for using this code directly with Keil uVision MDK.

Advanced Solutions Nederland is happy to announce that the ASNFD filtering Arm MDK5 software pack now avalailable for download! The filtering pack provides MDK users with an easy way of ASN’s IP.

Keil MDK is the most comprehensive software development solution for Arm-based microcontrollers. For MDK, additional software components and support for microcontroller devices is provided by software packs. Download here

Modern embedded processors, software frameworks and design tooling now allow engineers to apply advanced measurement concepts to smart factories as part of the I4.0 revolution.

In recent years, PM (predictive maintenance) of machines has received great attention, as factories look to maximise their production efficiency while at the same time retaining the invaluable skills of experienced foremen and production workers.

Traditionally, a foreman would walk around the shop floor and listen to the sounds a machine would make to get an idea of impending failure. With the advent of I4.0 AIoT technology, microphones, edge DSP algorithms and ML may now be employed in order to ‘listen’ to the sounds a machine makes and then make a classification and prediction.

One of the major challenges is how to make a computer hear like a human. In this article we will discuss how sound weighting curves can make a computer hear like a human, and how they can be deployed to an Arm Cortex-M microcontroller for use in an AIoT application.

Physics of the human ear

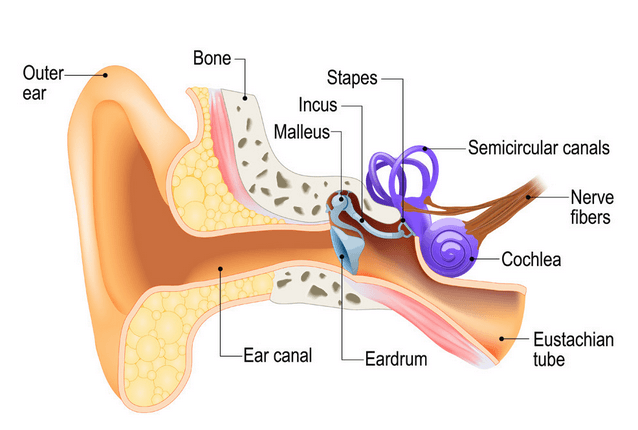

An illustration of the human ear shown below. As seen, the basic task of the ear is to translate sound (air vibration) into electrical nerve impulses for the brain to interpret.

The ear achieves this via three bones (Stapes, Incus and Malleus) that act as a mechanical amplifier for vibrations received at the eardrum. These amplified sounds are then passed onto the Cochlea via the Oval window (not shown).

The Cochlea (shown in purple) is filled with a fluid that moves in response to the vibrations from the oval window. As the fluid moves, thousands of nerve endings are set into motion. These nerve endings transform sound vibrations into electrical impulses that travel along the auditory nerve fibres to the brain for analysis.

Modelling perceived sound

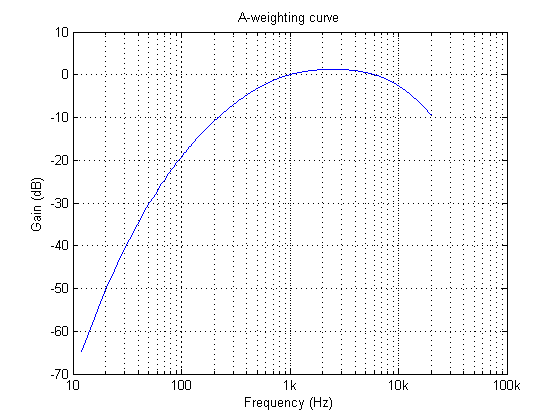

Due to complexity of the fluidic mechanical construction of the human auditory system, low and high frequencies are typically not discernible. Researchers over the years have found that humans are most perceptive to sounds in the 1-6kHz range, although this range varies according to the subject’s physical health.

This research led to the definition of a set of weighting curves: the so-called A, B, C and D weighting curves, which equalises a microphone’s frequency response. These weighting curves aim to bring the digital and physical worlds closer together by allowing a computerised microphone-based system to hear like a human.

The A-weighing curve is the most widely used as it is mandated by IEC-61672 to be fitted to all sound level meters. The B and D curves are hardly ever used, but C-weighting may be used for testing the impact of noise in telecoms systems.

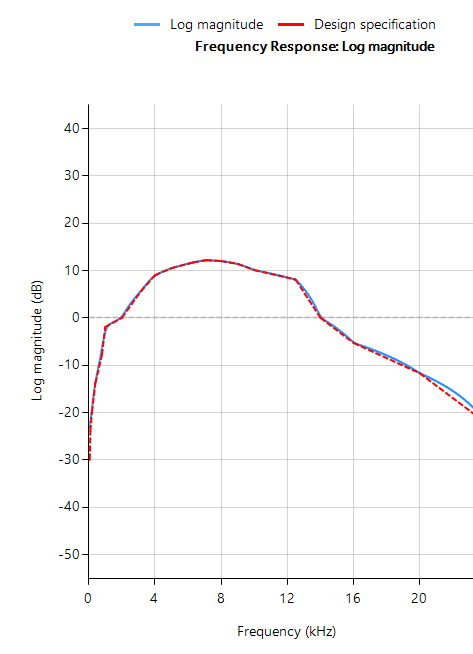

The frequency response of the A-weighting curve is shown above, where it can be seen that sounds entering our ears are de-emphasised below 500Hz and are most perceptible between 0.5-6kHz. Notice that the curve is unspecified above 20kHz, as this exceeds the human hearing range.

ASN FilterScript

ASN’s FilterScript symbolic math scripting language offers designers the ability to take an analog filter transfer function and transform it to its digital equivalent with just a few lines of code.

The analog transfer functions of the A and C-weighting curves are given below:

\(H_A(s) \approx \displaystyle{7.39705×10^9 \cdot s^4 \over (s + 129.4)^2\quad(s + 676.7)\quad (s + 4636)\quad (s + 76655)^2}\)

\(H_C(s) \approx \displaystyle{5.91797×10^9 \cdot s^2\over(s + 129.4)^2\quad (s + 76655)^2}\)

These analog transfer functions may be transformed into their digital equivalents via the bilinear() function. However, notice that \(H_A(s) \) requires a significant amount of algebracic manipulation in order to extract the denominator cofficients in powers of \(s\).

Convolution

A simple trick to perform polynomial multiplication is to use linear convolution, which is the same algebraic operation as multiplying two polynomials together. This may be easily performed via FilterScript’s conv() function, as follows:

y=conv(a,b);

As a simple example, the multiplication of \((s^2+2s+10)\) with \((s+5)\), would be defined as the following three lines of FilterScript code:

a={1,2,10};

b={1,5};

y=conv(a,b);

which yields, 1 7 20 50 or \((s^3+7s^2+20s+50)\)

For the A-weighting curve Laplace transfer function, the complete FilterScript code is given below:

ClearH1; // clear primary filter from cascade

Main() // main loop

a={1, 129.4};

b={1, 676.7};

c={1, 4636};

d={1, 76655};

aa=conv(a,a); // polynomial multiplication

dd=conv(d,d);

aab=conv(aa,b);

aabc=conv(aab,c);

Na=conv(aabc,dd);

Nb = {0 ,0 , 1 ,0 ,0 , 0, 0}; // define numerator coefficients

G = 7.397e+09; // define gain

Ha = analogtf(Nb, Na, G, "symbolic");

Hd = bilinear(Ha,0, "symbolic");

Num = getnum(Hd);

Den = getden(Hd);

Gain = getgain(Hd)/computegain(Hd,1e3); // set gain to 0dB@1kHz

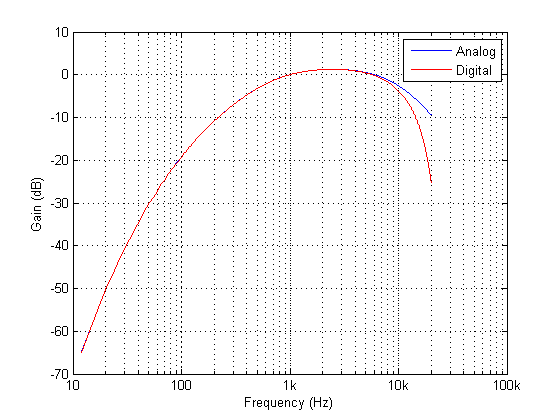

Frequency response of analog vs digital A-weighting filter for \(f_s=48kHz\). As seen, the digital equivalent magnitude response matches the ideal analog magnitude response very closely until \(6kHz\).

The ITU-R 486–4 weighting curve

Another weighting curve of interest is the ITU-R 486–4 weighting curve, developed by the BBC. Unlike the A-weighting filter, the ITU-R 468–4 curve describes subjective loudness for broadband stimuli. The main disadvantage of the A-weighting curve is that it underestimates the loudness judgement of real-world stimuli particularly in the frequency band from about 1–9 kHz.

Due to the precise definition of the 486–4 weighting curve, there is no analog transfer function available. Instead the standard provides a table of amplitudes and frequencies – see here. This specification may be directly entered into FilterScript’s firarb() function for designing a suitable FIR filter, as shown below:

ClearH1; // clear primary filter from cascade

ShowH2DM;

interface L = {10,400,10,250}; // filter order

Main()

// ITU-R 468 Weighting

A={-29.9,-23.9,-19.8,-13.8,-7.8,-1.9,0,5.6,9,10.5,11.7,12.2,12,11.4,10.1,8.1,0,-5.3,-11.7,-22.2};

F={63,100,200,400,800,1e3,2e3,3.15e3,4e3,5e3,6.3e3,7.1e3,8e3,9e3,1e4,1.25e4,1.4e4,1.6e4,2e4};

A={-30,A}; // specify arb response

F={0,F,fs/2};

Hd=firarb(L,A,F,"blackman","numeric");

Num=getnum(Hd);

Den={1};

Gain=getgain(Hd);

firarb() function for \(f_s=48kHz\)As seen, FilterScript provides the designer with a very powerful symbolic scripting language for designing weighting curve filters. The following discussion now focuses on deployment of the A-weighting filter to an Arm based processor via the tool’s automatic code generator. The concepts and steps demonstrated below are equally valid for FIR filters.

Automatic code generation to Arm processor cores via CMSIS-DSP

The ASN Filter Designer’s automatic code generation engine facilitates the export of a designed filter to Cortex-M Arm based processors via the CMSIS-DSP software framework.

The tool’s built-in analytics and help functions assist the designer in successfully configuring the design for deployment. Professional licence users may expedite the deployment by using the Arm deployment wizard that automates the steps described below.

Steps required for Educational licence users only

Before generating the code, the H2 filter (i.e. the filter designed in FilterScript) needs to be firstly re-optimised (transformed) to an H1 filter (main filter) structure for deployment. The options menu can be found under the P-Z tab in the main UI.

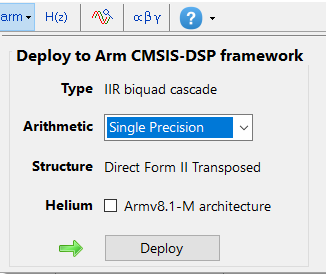

All floating point IIR filters designs must be based on Single Precision arithmetic and either a Direct Form I or Direct Form II Transposed filter structure. The Direct Form II Transposed structure is advocated for floating point implementation by virtue of its higher numerically accuracy.

Quantisation and filter structure settings can be found under the Q tab (as shown on the left). Setting Arithmetic to Single Precision and Structure to Direct Form II Transposed and clicking on the Apply button configures the IIR considered herein for the CMSIS-DSP software framework.

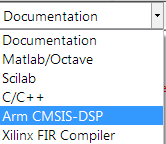

Select the Arm CMSIS-DSP framework from the selection box in the filter summary window:

The automatically generated C code based on the CMSIS-DSP framework for direct implementation on an Arm based Cortex-M processor is shown below:

As seen, the ASN Filter Designer’s automatic code generator generates all initialisation code, scaling and data structures needed to implement the A-weighting filter IIR filter via Arm’s CMSIS-DSP library. A detailed help tutorial is available by clicking on the Show me button.

Author

-

Sanjeev is a RTEI (Real-Time Edge Intelligence) visionary and expert in signals and systems with a track record of successfully developing over 26 commercial products. He is a Distinguished Arm Ambassador and advises top international blue chip companies on their AIoT/RTEI solutions and strategies for I5.0, telemedicine, smart healthcare, smart grids and smart buildings.

View all posts

Infinite impulse response (IIR) filters are useful for a variety of sensor measurement applications, including measurement noise removal and unwanted component cancellation, such as powerline interference. Although several practical implementations for the IIR exist, the Direct form II Transposed structure offers the best numerical accuracy for floating point implementation. However, when considering fixed point implementation on a microcontroller, the Direct Form I structure is considered to be the best choice by virtue of its large accumulator that accommodates any intermediate overflows. This application note specifically addresses IIR biquad filter design and implementation on a Cortex-M based microcontroller with the ASN Filter Designer for both floating point and fixed point applications via the Arm CMSIS-DSP software framework.

Details are also given (including a reference example project) regarding implementation of the IIR filter in Arm/Keil’s MDK industry standard Cortex-M microcontroller development kit.

Introduction

ASN Filter Designer provides engineers with a powerful DSP experimentation platform, allowing for the design, experimentation and deployment of complex IIR and FIR (finite impulse response) digital filter designs for a variety of sensor measurement applications. The tool’s advanced functionality, includes a graphical based real-time filter designer, multiple filter blocks, various mathematical I/O blocks, live symbolic math scripting and real-time signal analysis (via a built-in signal analyser). These advantages coupled with automatic documentation and code generation functionality allow engineers to design and validate a digital filter within minutes rather than hours.

The Arm CMSIS-DSP (Cortex Microcontroller Software Interface Standard) software framework is a rich collection of over sixty DSP functions (including various mathematical functions, such as sine and cosine; IIR/FIR filtering functions, complex math functions, and data types) developed by Arm that have been optimised for their range of Cortex-M processor cores.

The framework makes extensive use of highly optimised SIMD (single instruction, multiple data) instructions, that perform multiple identical operations in a single cycle instruction. The SIMD instructions (if supported by the core) coupled together with other optimisations allow engineers to produce highly optimised signal processing applications for Cortex-M based micro-controllers quickly and simply.

ASN Filter Designer fully supports the CMSIS-DSP software framework, by automatically producing optimised C code based on the framework’s DSP functions via its code generation engine.

Designing IIR filters with the ASN Filter Designer

ASN Filter Designer provides engineers with an easy to use, intuitive graphical design development platform for both IIR and FIR digital filter design. The tool’s real-time design paradigm makes use of graphical design markers, allowing designers to simply draw and modify their magnitude frequency response requirements in real-time while allowing the tool automatically fill in the exact specifications for them.

Consider the design of the following technical specification:

| Fs: | 500Hz |

| Passband frequency: | 0-40Hz |

| Type: | Lowpass |

| Method: | Elliptic |

| Stopband attenuation @ 125Hz: | ≥ 80 dB |

| Passband ripple: | < 0.1dB |

| Order: | Small as possible |

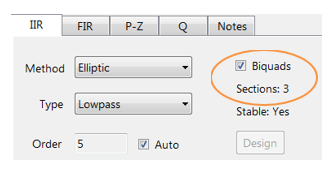

Graphically entering the specifications into the ASN Filter Designer, and fine tuning the design marker positions, the tool automatically designs the filter as a Biquad cascade (this terminology will be discussed in the following sections), automatically choosing the required filter order, and in essence – automatically producing the filter’s exact technical specification!

The frequency response of a 5th order IIR Elliptic Lowpass filter meeting the specifications is shown below:

This 5th order Lowpass filter will form the basis of the discussion presented herein.

Biquad IIR filters

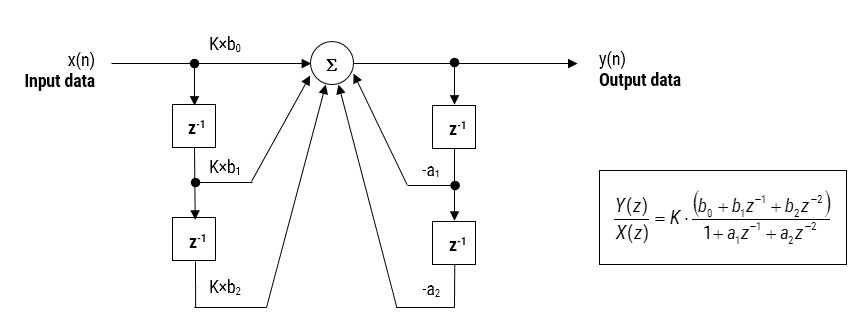

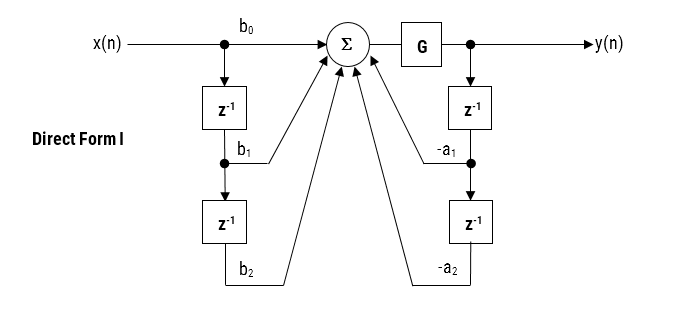

The IIR filter implementation discussed herein is said to be biquad, since it has two poles and two zeros as illustrated below in Figure 1. The biquad implementation is particularly useful for fixed point implementations, as the effects of quantization and numerical stability are minimised. However, the overall success of any biquad implementation is dependent upon the available number precision, which must be sufficient enough in order to ensure that the quantised poles are always inside the unit circle.

Figure 1: Direct Form I (biquad) IIR filter realization and transfer function.

Analysing Figure 1, it can be seen that the biquad structure is actually comprised of two feedback paths (scaled by \(a_1\) and \(a_2\)), three feed forward paths (scaled by \(b_0, b_1\) and \(b_2\)) and a section gain, \(K\). Thus, the filtering operation of Figure 1 can be summarised by the following simple recursive equation:

\(\displaystyle y(n)=K\times\Big[b_0 x(n) + b_1 x(n-1) + b_2 x(n-2)\Big] – a_1 y(n-1)-a_2 y(n-2)\)

Analysing the equation, notice that the biquad implementation only requires four additions (requiring only one accumulator) and five multiplications, which can be easily accommodated on any Cortex-M microcontroller. The section gain, \(K\) may also be pre-multiplied with the forward path coefficients before implementation.

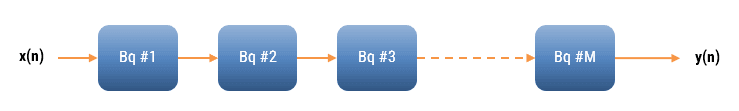

A collection of Biquad filters is referred to as a Biquad Cascade, as illustrated below.

The ASN Filter Designer can design and implement a cascade of up to 50 biquads (Professional edition only).

Floating point implementation

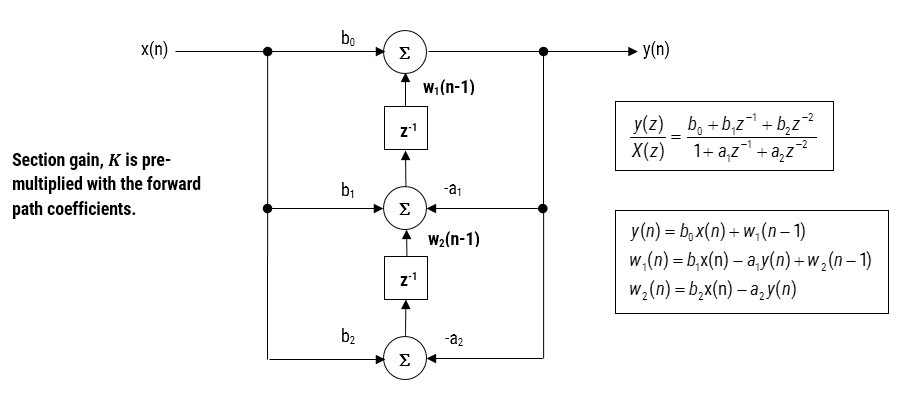

When implementing a filter in floating point (i.e. using double or single precision arithmetic) Direct Form II structures are considered to be a better choice than the Direct Form I structure. The Direct Form II Transposed structure is considered the most numerically accurate for floating point implementation, as the undesirable effects of numerical swamping are minimised as seen by analysing the difference equations.

Figure 2 – Direct Form II Transposed strucutre, transfer function and difference equations

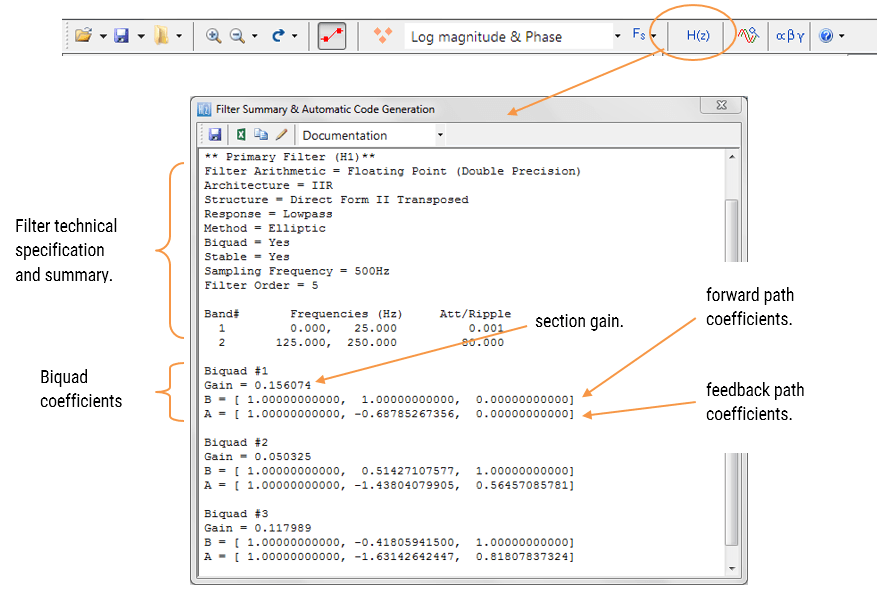

The filter summary (shown in Figure 3) provides the designer with a detailed overview of the designed filter, including a detailed summary of the technical specifications and the filter coefficients, which presents a quick and simple route to documenting your design.

The ASN Filter Designer supports the design and implementation of both single section and Biquad (default setting) IIR filters. However, as the CMSIS-DSP framework does not directly support single section IIR filters, this feature will not be covered in this application note.

The CMSIS-DSP software framework implementation requires sign inversion (i.e. flipping the sign) of the feedback coefficients. In order to accommodate this, the tool’s automatic code generation engine automatically flips the sign of the feedback coefficients as required. In this case, the set of difference equations become,

\(y(n)=b_0 x(n)+w_1 (n-1)\)

\(w_1 (n)= b_1 x(n)+a_1 y(n)+w_2 (n-1)\)

\(w_2 (n)= b_2 x(n)+a_2 y(n)\)

Figure 3: ASN filter designer: filter summary.

Automatic code generation to Arm processor cores via CMSIS-DSP

The ASN Filter Designer’s automatic code generation engine facilitates the export of a designed filter to Cortex-M Arm based processors via the CMSIS-DSP software framework. The tool’s built-in analytics and help functions assist the designer in successfully configuring the design for deployment.

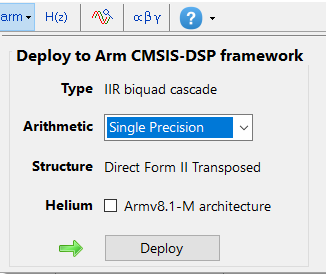

All floating point IIR filters designs should be based on Single Precision arithmetic and either a Direct Form I or Direct Form II Transposed filter structure, as this is supported by a hardware multiplier in the M4F, M7F, M33F and M55F cores. Although you may choose Double Precision, hardware support is only available in some M7F and M55F Helium devices. As discussed in the previous section, the Direct Form II Transposed structure is advocated for floating point implementation by virtue of its higher numerically accuracy.

Quantisation and filter structure settings can be found under the Q tab (as shown on the left). Setting Arithmetic to Single Precision and Structure to Direct Form II Transposed and clicking on the Apply button configures the IIR considered herein for the CMSIS-DSP software framework.

Select the Arm CMSIS-DSP framework from the selection box in the filter summary window:

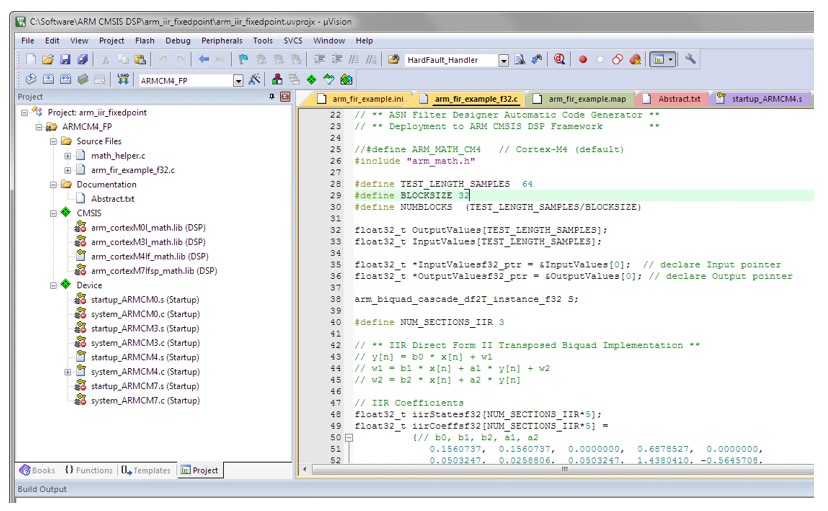

The automatically generated C code based on the CMSIS-DSP framework for direct implementation on an Arm based Cortex-M processor is shown below:

As seen, the automatic code generator generates all initialisation code, scaling and data structures needed to implement the IIR via the CMSIS-DSP library. This code may be directly used in any Cortex-M based development project – a complete Keil MDK example is available on Arm/Keil’s website. Notice that the tool’s code generator produces code for the Cortex-M4 core as default, please refer to the table below for the #define definition required for all supported cores.

ARM_MATH_CM0 | Cortex-M0 core. | ARM_MATH_CM4 | Cortex-M4 core. |

ARM_MATH_CM0PLUS | Cortex-M0+ core. | ARM_MATH_CM7 | Cortex-M7 core. |

ARM_MATH_CM3 | Cortex-M3 core. | ||

ARM_MATH_ARMV8MBL | ARMv8M Baseline target (Cortex-M23 core). | ||

ARM_MATH_ARMV8MML | ARMv8M Mainline target (Cortex-M33 core). |

Automatic code generation of complex coefficient IIR filters is currently not supported (see below for more information).

Arm deployment wizard

Professional licence users may expedite the deployment by using the Arm deployment wizard. The built in AI will automatically determine the best settings for your design based on the quantisation settings chosen.

The built in AI automatically analyses your complete filter cascade and converts any H2 or Heq filters into an H1 for implementation. A complex coefficient filter will be automatically converted to real filter for implementation.

Implementing the filter in Arm Keil’s MDK

As mentioned in the previous section, the code generated by the Arm CMSIS-DSP code generator may be directly used in any Cortex-M based development project tooling, such as Arm Keil’s industry standard μVision MDK (microcontroller development kit).

A complete μVision example IIR biquad filter project can be downloaded from Keil’s website, and as seen below is as simple as copying and pasting the code and making minor adjustments to the code.

The example project makes use of μVision’s powerful simulation capabilities, allowing for the evaluation of the IIR filter on M0, M3, M4 and M7 cores respectively. As an added bonus, μVision’s logic analyser may also be used, allowing for comparisons between the ASN Filter Designer’s signal analyser and the reality on a Cortex-M core.

Fixed point implementation

As aforementioned, the Direct Form I filter structure is the best choice for fixed point implementation. However, before implementing the difference equation on a fixed point processor, several important data scaling considerations must be taken into account. As the CMSIS-DSP framework only supports Q15 and Q31 data types for IIR filters, the following discussion relates to an implementation on a 16-bit word architecture, i.e. Q15.

Quantisation

In order to correctly represent the coefficients and input/output numbers, the system word length (16-bit for the purposes of this application note) is first split up into its number of integers and fractional components. The general format is given by:

Q Num of Integers.Fraction length

If we assume that all of data values lie within a maximum/minimum range of \(\pm 1\), we can use Q0.15 format to represent all of the numbers respectively. Notice that Q0.15 (or simply Q15) format represents a maximum of \(\displaystyle 1-2^{-15}=0.9999=0x7FFF\) and a minimum of \(-1=0x8000\) (two’s complement format).

The ASN Filter Designer may be configured for Fixed Point Q15 arithmetic by setting the Word length and Fractional length specifications in the Q Tab (see the configuration section for the details). However, one obvious problem that manifests itself for Biquads is the number range of the coefficients. As poles can be placed anywhere inside the unit circle, the resulting polynomial needed for implementation will often be in the range \(\pm 2\), which would require Q14 arithmetic. In order to overcome this issue, all numerator and denominator coefficients are scaled via a biquad Post Scaling Factor as discussed below.

Post Scaling Factor

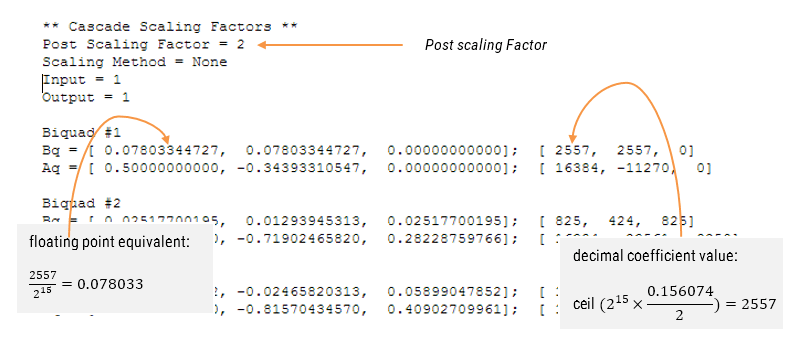

In order to ensure that coefficients fit within the Word length and Fractional length specifications, all IIR filters include a Post Scaling Factor, which scales the numerator and denominator coefficients accordingly. As a consequence of this scaling, the Post Scaling Factor must be included within the filter structure in order to ensure correct operation.

The Post scaling concept is illustrated below for a Direct Form I biquad implementation.

Figure 4: Direct Form I structure with post scaling.

Pre-multiplying the numerator coefficients with the section gain, \(K\), each coefficient can now be scaled by \(G\), i.e. \(\displaystyle b_0=\frac{b_0}{G}, b_1=\frac{b_1}{G}, a_1=\frac{a_1}{G}, a_2=\frac{a_2}{G}\) and etc. This now results in the following difference equation:

\(\displaystyle y(n)=G \times\Big [b_0 x(n) + b_1 x(n-1) + b_2 x(n-2) – a_1 y(n-1)-a_2 y(n-2)\Big]\)

All IIR structures implemented within the tool include the Post Scaling Factor concept. This scaling is mandatory for implementation via the Arm CMSIS-DSP framework – see the configuration section for more details.

Understanding the filter summary

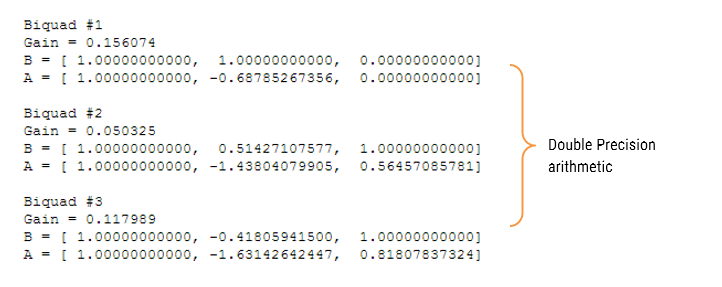

In order to fully understand the information presented in the ASN Filter Designer filter summary, the following example illustrates the filter coefficients obtained with Double Precision arithmetic and with Fixed Point Q15 quantisation.

Applying Fixed Point Q15 arithmetic (note the effects of quantisation on the coefficient values):

Configuring the ASN Filter Designer for Fixed Point arithmetic

In order to implement an IIR fixed point filter via the CMSIS-DSP framework, all designs must be based on Fixed Point arithmetic (either Q15 or Q31) and the Direct Form I filter structure.

Quantisation and filter structure settings can be found under the Q tab (as shown on the left): Setting Arithmetic to Fixed Point and Structure to Direct Form I and clicking on the Apply button configures the IIR considered herein for the CMSIS-DSP software framework.

The Post Scaling Factor is actually implemented in the CMSIS-DSP software framework as \( \log_2 G\) (i.e. a shift left scaling operation as depicted in Figure 4).

Built in analytics: the tool will automatically analyse the cascade’s filter coefficients and choose an appropriate scaling factor. As seen above, as the largest minimum value is -1.63143, thus, a Post Scaling Factor of 2 is required in order to ‘fit’ all of the coefficients into Q15 arithmetic.

Comparing spectra obtained by different arithmetic rules

In order to improve clarity and overall computation speed, the ASN Filter Designer only displays spectra (i.e. magnitude, phase etc.) based on the current arithmetic rules. This is somewhat different to other tools that display multi-spectra obtained by (for example) Fixed Point and Double Precision arithmetic. For any users wishing to compare spectra you may simply switch between arithmetic settings by changing the Arithmetic method. The designer will then automatically re-compute the filter coefficients using the selected arithmetic rules and the current technical specification. The chart will then be updated using the current zoom settings.

Automatic code generation to the Arm CMSIS-DSP framework

As with floating point arithmetic, select the Arm CMSIS-DSP framework from the selection box in the filter summary window:

The automatically generated C code based on the CMSIS-DSP framework for direct implementation on an Arm based Cortex-M processor is shown below:

As with the floating point filter, the automatic code generator generates all initialisation code, scaling and data structures needed to implement the IIR via the CMSIS-DSP library. This code may be directly used in any Cortex-M based development project – a complete Keil MDK example is available on Arm/Keil’s website. Notice that the tool’s code generator produces code for the Cortex-M4 core as default, please refer to the table below for the #define definition required for all supported cores.

ARM_MATH_CM0 | Cortex-M0 core. | ARM_MATH_CM4 | Cortex-M4 core. |

ARM_MATH_CM0PLUS | Cortex-M0+ core. | ARM_MATH_CM7 | Cortex-M7 core. |

ARM_MATH_CM3 | Cortex-M3 core. | ||

ARM_MATH_ARMV8MBL | ARMv8M Baseline target (Cortex-M23 core). | ||

ARM_MATH_ARMV8MML | ARMv8M Mainline target (Cortex-M33 core). |

The main test loop code (not shown) centres around the arm_biquad_cascade_df2T_f32() function, which performs the filtering operation on a block of input data.

Complex coefficient IIR filters are currently not supported.

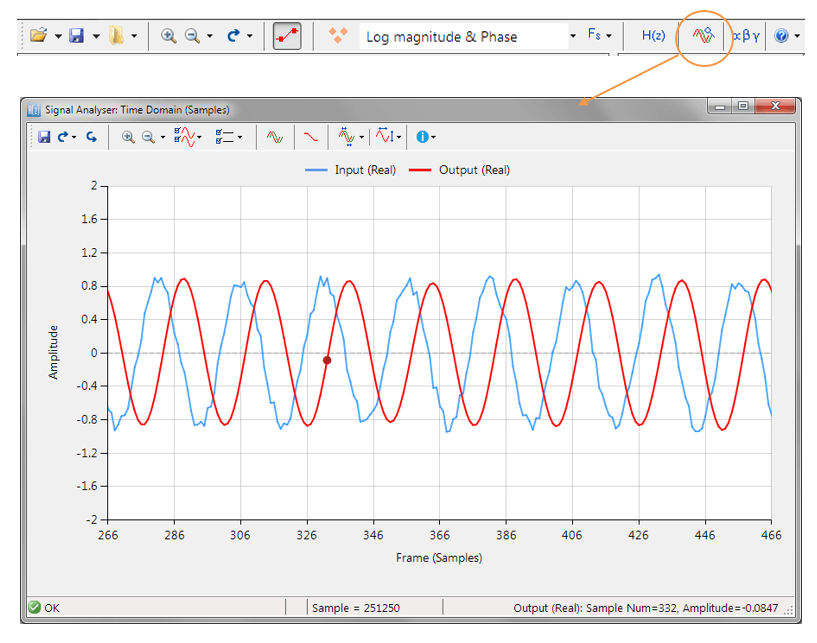

Validating the design with the signal analyser

A design may be validated with the signal analyser, where both time and frequency domain plots are supported. A comprehensive signal generator is fully integrated into the signal analyser allowing designers to test their filters with a variety of input signals, such as sine waves, white noise or even external test data.

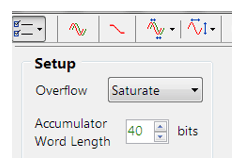

For Fixed Point implementations, the tool allows designers to specify the Overflow arithmetic rules as: Saturate or Wrap. Also, the Accumulator Word Length may be set between 16-40 bits allowing designers to quickly find the optimum settings to suit their application.

Extra resources

- Digital signal processing: principles, algorithms and applications, J.Proakis and D.Manoloakis

- Digital signal processing: a practical approach, E.Ifeachor and B.Jervis.

- Digital filters and signal processing, L.Jackson.

- Step by step video tutorial of designing an IIR and deploying it to Keil MDK uVision.

- Implementing Biquad IIR filters with the ASN Filter Designer and the Arm CMSIS-DSP software framework (ASN-AN025)

- Keil MDK uVision example IIR filter project

Author

-

Sanjeev is a RTEI (Real-Time Edge Intelligence) visionary and expert in signals and systems with a track record of successfully developing over 26 commercial products. He is a Distinguished Arm Ambassador and advises top international blue chip companies on their AIoT/RTEI solutions and strategies for I5.0, telemedicine, smart healthcare, smart grids and smart buildings.

View all posts

Did you know that there are 23 billion IoT embedded devices currently deployed around the world? This figure is expected to grow to a whopping 1 trillion devices by 2050!

Less known, is that 80% of IoT devices are based around Arm’s Cortex-M microcontroller technology. Sometimes clients ask us if we support their Arm Cortex-M based demo-board of choice. The answer is simply: yes!

200+ IC vendors supported

The ASN Filter Designer has an automatic code generator for Arm Cortex-M cores, which means that we support virtually every Arm based demo-board: ST, Cypress, NXP, Analog Devices, TI, Microchip/Atmel and over 200+ other manufacturers. Our compatibility with Arm’s free CMSIS-DSP software framework removes the frustration of implementing complicated digital filters in your IoT application – leaving you with code that is optimal for Cortex-M devices and that works 100% of the time.

The Arm Cortex-M family of microcontrollers are an excellent match for IoT applications. Some of the advantages include:

- Low power and cost – essential for IoT devices

- Microcontroller with DSP functionality all-in-one

- Embedded hardware security functionality

- Cortex-M4 and M7 cores with hardware floating support (enhanced microcontrollers)

- Freely available CMSIS-DSP C library: supporting over 60 signal processing functions

Automatic code generation for Arm’s CMSIS-DSP software framework

Simply load your sensor data into the ASN Filter Designer signal analyser and perform a detailed analysis. After identifying the wanted and unwanted components of your signal, design a filter and test the performance in real-time on your test data. Export the designed design to Arm MDK, C/C++ or integrate the filter into your algorithm in another domain, such as in Matlab, Python, Scilab or Labview.

Use the tool in your RAD (rapid application development) process, by taking advantage of the automatic code generation to Arm’s CMSIS-DSP software framework, and quickly integrate the DSP filter code into your main application code.

Let the tool analyse your design, and automatically generate fully compliant code for either the M0, M0+, M3, M4 and the newer M23 and M33 Cortex cores. Deploy your design within minutes rather than hours.

Proud Arm knowledge partner

We are proud that we are an Arm knowledge partner! As an Arm DSP knowledge partner, we will be kept informed of their product roadmap and progress for the coming years.

Try it for yourself and see the benefits that the ASN Filter Designer can offer your organisation by cutting your development costs by up to 75%!

How to choose between analog signal processing (ASP) and digital signal processing (DSP). How too chose for ASP or DSP; analog filters or digital filters?

Drones and DC motor control – How the ASN Filter Designer can save you a lot of time and effort

Drones are one of the golden nuggets in IoT. No wonder, they can play a pivotal role in congested cities and far away areas for delivery. Further, they can be a great help to give an overview of a large area or places which are difficult or dangerous to reach. However, most of the technology is still in its experimental stage.

Because drones have a lot of sensors, Advanced Solutions Nederland did some research on how drone producing companies have solved questions regarding their sensor technology, especially regarding DC motor control.

Until now: solutions developed with great difficulty

We found out that most producers spend weeks or even months on finding solutions for their sensor technology challenges. With the ASN Filter Designer, he/she could have come to a solution within days or maybe even hours. Besides, we expect that the measurement would be better too.

The biggest time coster is that until now algorithms were developed by handwork, i.e. they were developed in a lab environment and then tested in real-life. With the result of the test, the algorithm would be tweaked again until the desired results were reached. However, yet another challenge stems from the fact that a lab environment is where testing conditions are stable, so it’s very hard to make models work in real life. These steps result in rounds and rounds of ‘lab development’ and ‘real life testing’ in order to make any progress -which isn’t ideal!

How the ASN Filter Designer can help save a lot of time and effort

The ASN Filter Designer can help a lot of time in the design and testing of algorithms in the following ways:

- Design, analyse and implement filters for drone sensor applications with real-time feedback and our powerful signal analyser.

- Design filters for speed and positioning control for sensorless BLDC (brushless DC) motor applications.

- Speed up deployment to Arm Cortex-M embedded processors.

Real-time feedback and powerful signal analyser

One of the key benefits of the ASN Filter Designer and signal analyser is that it gives real-time feedback. Once an algorithm is developed, it can easily be tested on real-life data. To analyse the real-life data, the ASN Filter Designer has a powerful signal analyser in place.

Design and analyse filters the easy way

You can easily design, analyse and implement filters for a variety of drone sensor applications, including: loadcells, strain gauges, torque, pressure, temperature, vibration, and ultrasonic sensors and assess their dynamic performance in real-time for a variety of input conditions. With the ASN Filter Designer, you don’t have do to any coding yourself or break your head with specifications: you just have to draw the filter magnitude specification and the tool will calculate the coefficients itself.

Speed up deployment

Perform detailed time/frequency analysis on captured test datasets and fine-tune your design. Our Arm CMSIS-DSP and C/C++ code generators and software frameworks speed up deployment to a DSP, FPGA or micro-controller.

An example: designing BLDC motor control algorithms

BLDC (brushless DC) BLDC motors have found use in a variety of application areas, including: robotics, drones and cars. They have significant advantages over brushed DC motors and induction motors, such as: better speed-torque characteristics, high reliability, longer operating life, noiseless operation, and reduction of electromagnetic interference (EMI).

One advantage of BLDC motor control compared to standard DC motors is that the motor’s speed can be controlled very accurately using six-step commutation, making it a good choice for precision motion applications, such as robotics and drones.

Sensorless back-EMF and digital filtering

For most applications, monitoring of the back-EMF (back-electromotive force) signal of the unexcited phase winding is easier said than done, since it has significant noise distortion from PWM (pulse width modulation) commutation from the other energised windings. The coupling between the motor parameters, especially inductances, can induce ripple in the back-EMF signal that is synchronous with the PWM commutation. As a consequence, this induced ripple on the back EMF signal leads to faulty commutation. Thus, the measurement challenge is how to accurately measure the zero-crossings of the back-EMF signal in the presence of PWM signals?

A standard solution is to use digital filtering, i.e. IIR, FIR or even a median (majority) filter. However, the challenge for most designers is how to find the best filter type and optimal filter specification for the motor under consideration.

The solution

The ASN Filter Designer allows engineers to work on speed and position sensorless BLDC motor control applications based on back-EMF filtering to easily experiment and see the filtering results on captured test datasets in real-time for various IIR, FIR and median (majority filtering) digital filtering schemes. The tool’s signal analyser implements a robust zero-crossings detector, allowing engineers to evaluate and fine-tune a complete sensorless BLDC control algorithm quickly and simply.

So, if you have a measurement problem, ask yourself:

Can I save time and money, and reduce the headache of design and implementation with an investment in new tooling?

Our licensing solutions start from just 125 EUR for a 3-month licence.

Find out what we can do for you, and learn more by visiting the ASN Filter Designer’s product homepage.

It’s estimated that the global smart sensor market will have over 50 billion smart devices in 2020. At least 80% of these IoT/IIoT smart sensors (temperature, pressure, gas, image, motion, loadcells) will use Arm’s Cortex-M technology – where the largest growth is in smart Image sensors (ADAS) & smart Temperature sensors (HVAC).

IoT sensor measurement challenge

The challenge for most, is that many sensors used in these applications require a little bit of filtering in order to clean the measurement data in order to make it useful for analysis.

Let’s have a look at what sensor data really is…. All sensors produce measurement data. These measurement data contain two types of components:

- Wanted components, i.e. information what we want to know

- Unwanted components, measurement noise, 50/60Hz powerline interference, glitches etc – what we don’t want to know

Unwanted components degrade system performance and need to be removed.

So, how do we do it?

DSP means Digital Signal Processing and is a mathematical recipe (algorithm) that can be applied to IoT sensor measurement data in order to clean it and make it useful for analysis.

But that’s not all! DSP algorithms can also help in analysing data, producing more accurate results for decision making with ML (machine learning). They can also improve overall system performance with existing hardware (no need to redesign your hardware – a massive cost saving!), and can reduce the data sent off to the cloud by pre-analysing data and only sending what is necessary.

Nevertheless, DSP has been considered by most to be a black art, limited only to those with a strong academic mathematical background. However, for many IoT/IIoT applications, DSP has been become a must in order to remain competitive and obtain high performance with relatively low cost hardware.

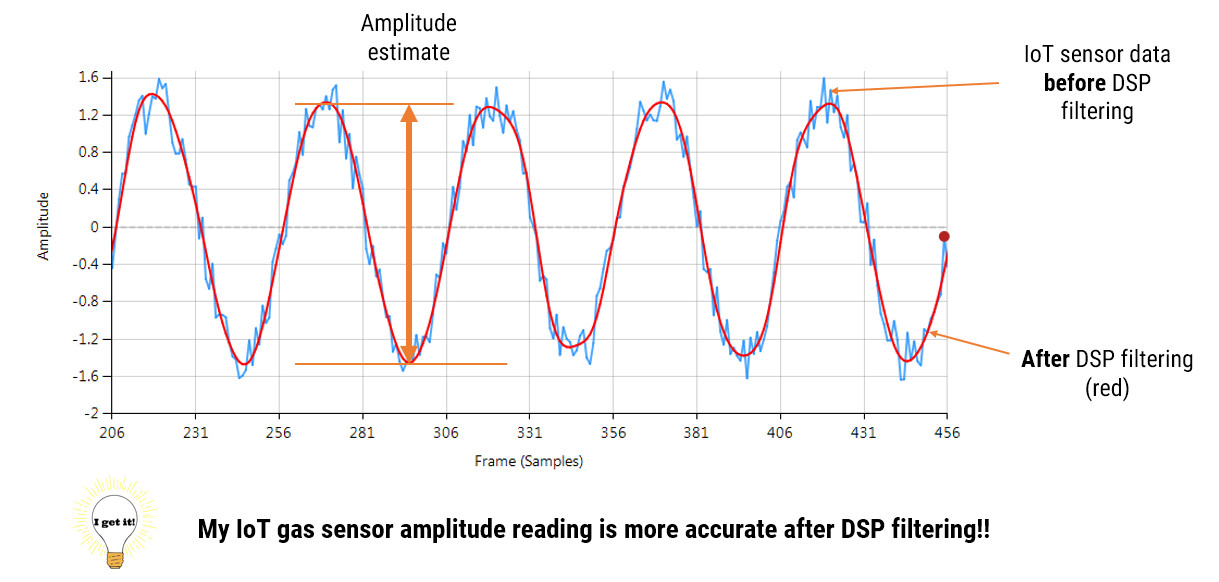

Do you have an example?

Consider the following application for gas sensor measurement (see the figure below). The requirement is to determine the amplitude of the sinusoid in order to get an estimate of gas concentration (bigger amplitude, more gas concentration etc). Analysing the figure, it is seen that the sinusoid is corrupted with measurement noise (shown in blue), and any estimate based on the blue signal will have a high degree of uncertainty about it – which is not very useful if getting an accurate reading of gas concentration!

Algorithms clean the sensor data

After ‘cleaning’ the sinusoid (red line) with a DSP filtering algorithm, we obtain a much more accurate and usable signal which helps us in estimating the amplitude/gas concentration. Notice how easy it is to determine the amplitude of red line.

This is only a snippet of what is possible with DSP algorithms for IoT/IIoT applications, but it should give you a good idea as to the possibilities of DSP.

How do I use this in my IoT application?

As mentioned at the beginning of this article, 80% of IoT smart sensor devices are deployed on Arm’s Cortex-M technology. The Arm Cortex-M4 is a very popular choice with hundreds of silicon vendors, as it offers DSP functionality traditionally found in more expensive DSPs. Arm and its partners provide developers with easy to use tooling and a free software framework (CMSIS-DSP) in order to get you up and running within minutes.

Author

-

Sanjeev is a RTEI (Real-Time Edge Intelligence) visionary and expert in signals and systems with a track record of successfully developing over 26 commercial products. He is a Distinguished Arm Ambassador and advises top international blue chip companies on their AIoT/RTEI solutions and strategies for I5.0, telemedicine, smart healthcare, smart grids and smart buildings.

View all posts

With the advent of smart cities, and society’s obsession of ‘being connected’, data networks have been overloaded with thousands of IoT sensors sending their data to the cloud, needing massive and very expensive computing resources to crunch the data.

Is it really a problem?

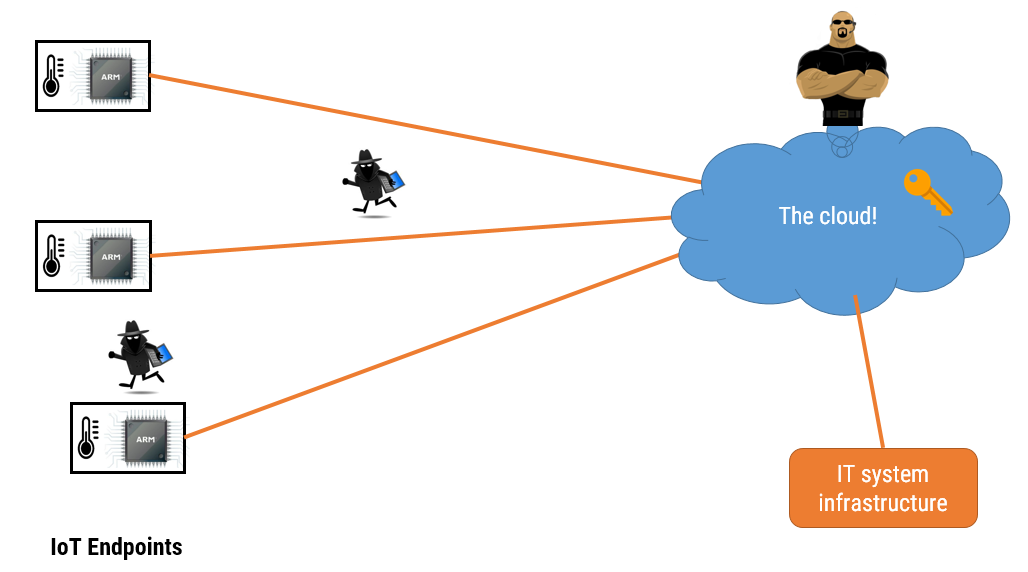

The collection of all these smaller IoT data streams (from smart sensors), has ironically resulted in a big data challenge for IT infrastructures in the cloud which need to process

massive datasets – as such there is no more room for scalability. The situation is further complicated with the fact, that a majority of sensor data is coming from remote locations, which also presents a massive security risk.

It’s estimated that the global smart sensor market will have over 50 billion smart devices in 2020. At least 80% of these IoT/IIoT smart sensors (temperature, pressure, gas, image, motion, loadcells) will use Arm’s Cortex-M technology, but have little or no smart data reduction or security implemented.

The current state of play

The modern IoT eco system problem is three-fold:

- Endpoint security

- Data reduction

- Data quality

Namely, how do we reduce our data that we send to the cloud, ensure that the data is genuine and how do ensure that our Endpoint (i.e. the IoT sensor) hasn’t been hacked?

The cloud is not infallible!

Traditionally, many system designers have thrown the problem over to the cloud. Data is sent from IoT sensors via a data network (Wifi, Bluetooth, LoRa etc) and is then encrypted in the cloud. Extra services in the cloud then perform data analysis in order to extract useful data.

So, what’s the problem then?

This model doesn’t take into account invalid sensor data. A simple example of this, could be glue failing on a temperature sensor, such that it’s not bonded to the motor or casing that it’s monitoring. The sensor will still give out temperature data, but it’s not valid for the application.

As for data reduction – the current model is ok for a few sensors, but when the network grows (as is the case with smart cities), the solution becomes untenable, as the cloud is overloaded with data that it needs to process.

No endpoint security, i.e. the sensor could be hacked, and the hacker could send fake data to the cloud, which will then be encrypted and passed onto the ML (machine learning) algorithm as genuine data.

What’s the solution?

Algorithms, algorithms….. and in built security blocks.

Over the last few years, hundreds of silicon vendors have been placing security IP blocks into their silicon together with a high performance Arm Cortex-M4 core. These so called enhanced micro-controllers offer designers a low cost and efficient solution for IoT systems for the foreseeable future.

A lot can be achieved by pre-filtering sensor data, checking it and only sending what is neccessary to the cloud. However, as with so many things, knowledge of security and algorithms are paramount for success.

Advanced Solutions Nederland B.V.

Lipperkerstraat 146

751DD Enschede

The Netherlands

General enquiries: info@advsolned.com

Technical support: support@advsolned.com

Sales enquiries: sales@advsolned.com

© 2026 Advanced Solutions Nederland B.V.

Privacy Policy | Disclaimer